Hardware-Optimized Trotterization for Heisenberg Model Quantum Simulation

The research tackles the challenge of simulating quantum dynamics using Trotter decomposition, which typically produces deep circuits that exceed the capabilities of current quantum hardware. By leveraging the symmetry of the Hamiltonian, the authors developed a hardware-efficient method for simulating the 3-site Heisenberg model, significantly reducing circuit depth. Implemented on IBM’s ibmq_jakarta and combined with error mitigation strategies, this approach achieved high-fidelity time-evolution simulations. This work showcases practical advancements in quantum simulation, overcoming hardware limitations to improve the accuracy and feasibility of modeling complex quantum systems.

Researchers Bo Yang and Naoki Negishi from the University of Tokyo have developed a novel symmetry-aware Trotterization technique specifically designed for simulating the Heisenberg model on IBM quantum hardware. By exploiting the intrinsic symmetries of the Hamiltonian, their method significantly reduces circuit depth, improving simulation accuracy.

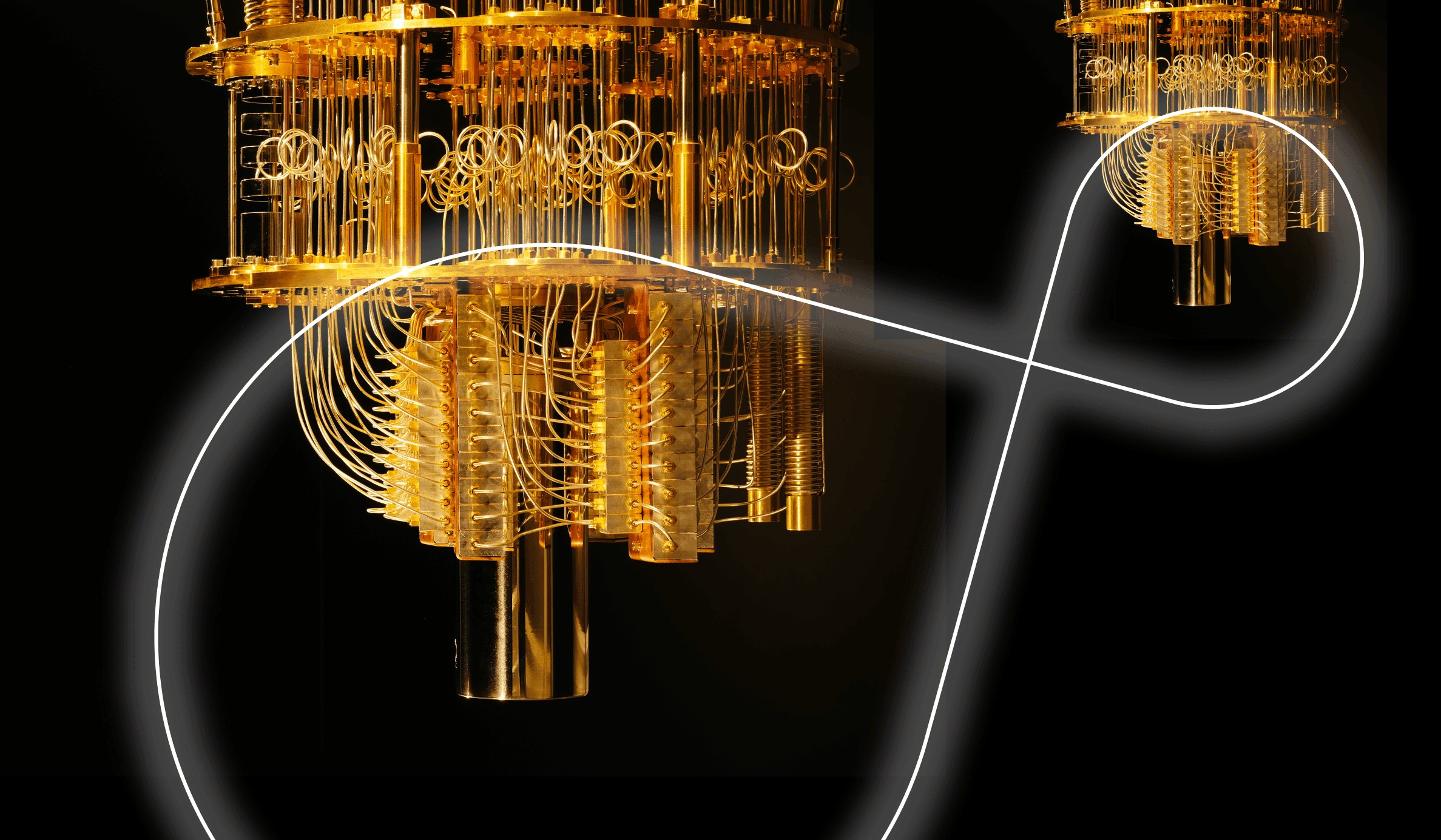

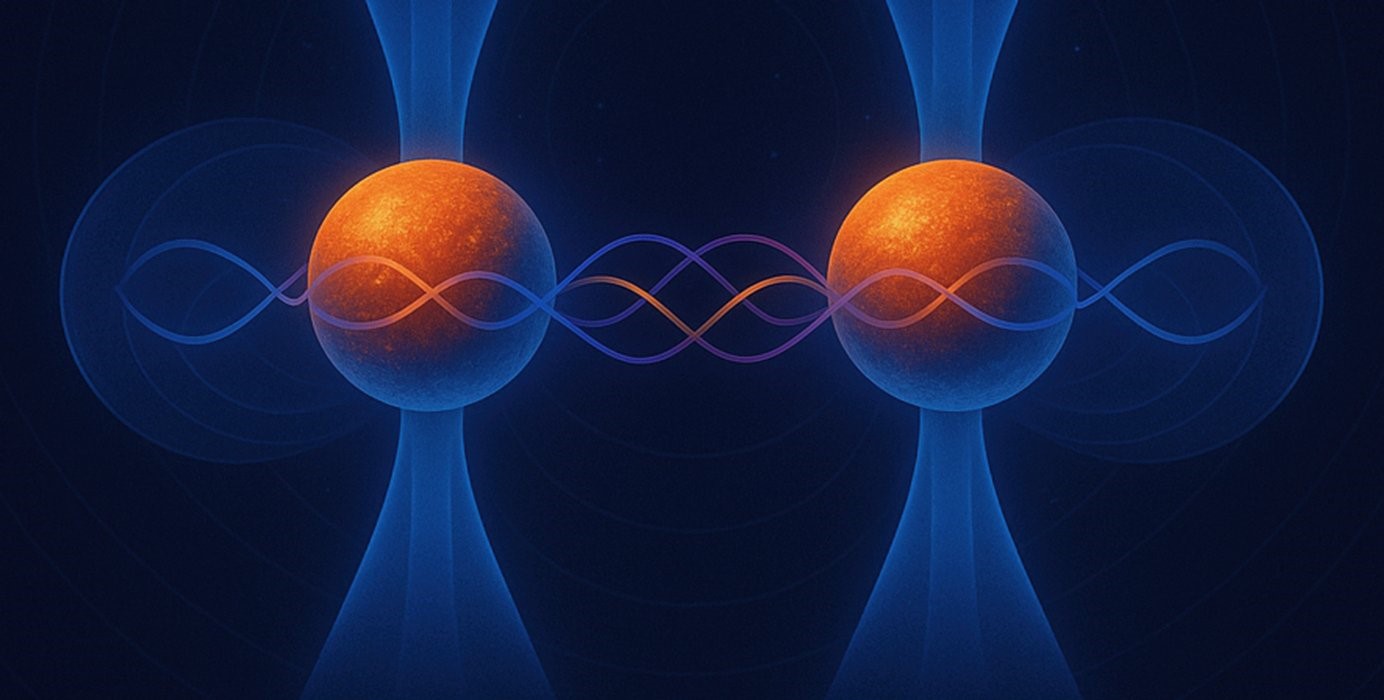

Figure 1. Hardware-Efficient Trotterization for Heisenberg Model Simulation

They tested this approach on IBM’s ibmq_jakarta device, incorporating advanced error mitigation strategies like zero-noise extrapolation and readout error correction. The results showed high-fidelity simulation of the Heisenberg model’s time evolution, demonstrating the method’s effectiveness and practicality. Figure 1 shows Hardware-Efficient Trotterization for Heisenberg Model Simulation.

Yang and Negishi’s work advances quantum simulation by emphasizing the power of leveraging system symmetries to optimize quantum algorithms, marking a key step toward more efficient and scalable quantum computing solutions.

Optimizing Quantum Circuits to Reduce Complexity for Efficient Simulations

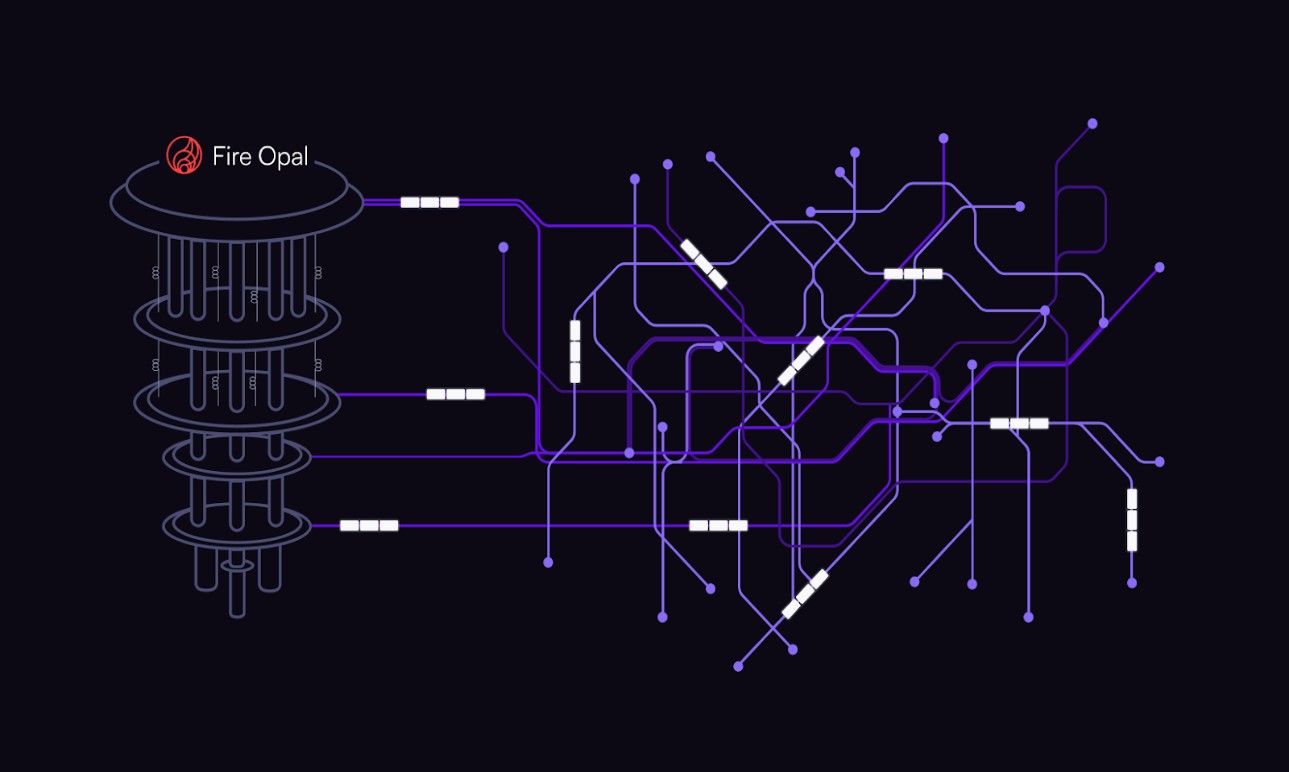

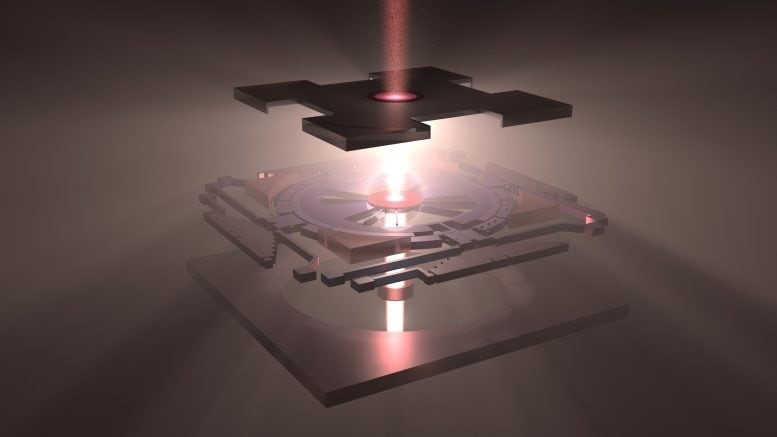

This research tackles the challenge of optimizing quantum circuits for simulating the Heisenberg model on IBM’s Jakarta quantum device, focusing on efficient resource use to improve accuracy and reduce errors. The team employs strategic partial Hamiltonian transformations and selective Trotter-axis choices to minimize the number of CNOT gates by enabling gate cancellations between consecutive Trotter steps, effectively reducing circuit depth.

They further enhance efficiency using Qiskit’s transpiler at its highest optimization level, which applies techniques like gate cancellation, decomposition, and reordering to produce constant-depth circuits suitable for execution on noisy hardware. The circuit is carefully mapped onto specific physical qubits (5, 3, 1) on the Jakarta device, chosen based on the device’s error profile to minimize noise and improve fidelity.

This combined approach of deliberate circuit design and hardware-aware automated optimization balances the number of Trotter steps with circuit complexity, enabling efficient and reliable quantum simulations despite current hardware limitations. It exemplifies how integrating system knowledge with advanced optimization tools can significantly advance practical quantum computing applications.

Optimized Quantum Circuits Cut CNOT Gates for Greater Efficiency

This study centers on optimizing quantum circuits for near-term quantum computing applications, focusing on reducing CNOT gates to improve efficiency and reliability. By implementing targeted Trotter steps and partial Hamiltonian transformations, the researchers demonstrated effective strategies using a 5-qubit system, showcasing the potential for more streamlined circuit designs.

They leveraged Qiskit’s transpiler, as detailed in Appendix B, to further refine the circuits by compiling high-level instructions into optimized low-level pulse sequences. An optimized circuit diagram (Figure 10) illustrates these improvements.

The research also explored practical implementation on IBM’s Jakarta quantum device, carefully selecting physical qubits (5, 3, and 1) mapped to virtual qubits (0, 1, and 2), taking into account device-specific error rates and connectivity to maximize performance.

Overall, the work highlights the significance of strategic circuit optimization combined with hardware-aware mapping, laying the groundwork for enhancing quantum computing efficiency on current quantum hardware.

Hardware-Aware Optimization Simplifies Quantum Circuits for Greater Efficiency

The study introduces an effective method for building efficient quantum circuits customized for specific Hamiltonians. By decomposing the Hamiltonian into subsets and applying partial transformations strategically during Trotter steps, the approach significantly reduces circuit depth and complexity [1]. Leveraging Qiskit’s transpiler alongside hardware-aware optimizations enhances overall efficiency, while mapping virtual qubits to physical qubits based on noise profiles helps minimize execution errors.

Future research could focus on extending this technique to more complex Hamiltonians and diverse quantum architectures [1]. Additionally, exploring adaptive qubit mappings that respond to real-time noise fluctuations may further boost circuit performance and reliability.

References:

- https://quantumzeitgeist.com/hardware-efficient-trotterization-for-quantum-simulation-of-the-heisenberg-model/

Cite this article:

Janani R (2025), Hardware-Optimized Trotterization for Heisenberg Model Quantum Simulation, AnaTechMaz, pp.265