Overview of the tiger SHARC Processor

Analog Devices TigerSHARC processors deliver industry-leading performance density for multiprocessing applications with peak performance well above one billion floating-point operations per second. They are ideal for applications involving automotive, motor and power control, process control, security and surveillance, and test and measurement. [1]

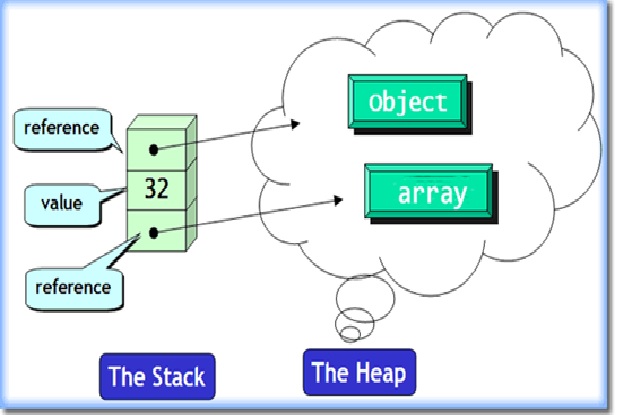

Figure 1. Overview of the tiger SHARC Processor

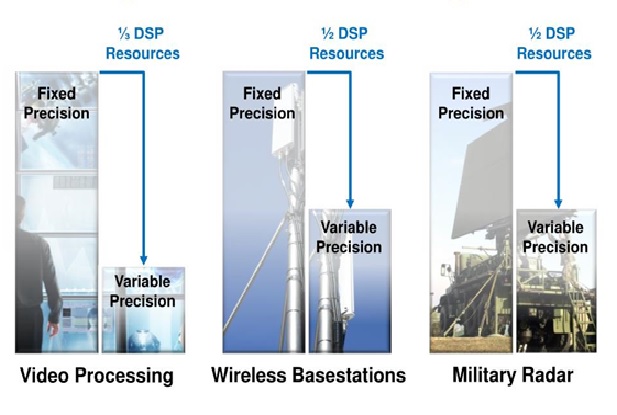

Figure 1 shows the TigerSHARC DSP is an ultra high-performance static superscalar architecture that is optimized for tele-communications infrastructure and other computationally demanding applications. This unique architecture combines elements of RISC, VLIW, and standard DSP processors to provide native support for 8, 16, and 32-bit fixed, as well as floating-point data types on a single chip.

Large on-chip memory, extremely high internal and external bandwidths and dual compute blocks provide the necessary capabilities to handle a vast array of computationally demanding, large signal processing tasks.

The word "SHARC" implies Super Harvard ARChitecture. The SHARC architecture has been improved greatly and the most powerful DSP today known has been implemented by Analog Devices and due to the high performance it yields it is called "Tiger" SHARC. The first implementation of the Tiger SHARC architecture is in a 0.25 micron, five level metal process at 150 MHz core clock speed. It delivers 900 MFlops (10 to the power 9 floating point operations per second) of single precision floating point performance or 3.6 GOPS of 16-bit arithmetic performance. It sustains an internal data bandwidth of 7.2 Gbytes /sec. [2]

Features

- Static superscalar DSPs

- Can execute simultaneously from one to four 32-bit instructions encoded in a single instruction line

- ADSP-TS20xS family provides a total memory bandwidth of 32 Gbytes/second, enabling the core and I/O to access twelve 32-bit data words four 32-bit instructions per cycle.

- ADSP-TS20xS family has three memory variants

- ADSP-TS201S has 24Mbits of on-chip embedded DRAM memory, divided into six blocks of 4Mbits (128K words x 32-bits)

- ADSP-TS202S has 12Mbits of on-chip embedded DRAM memory, divided into six blocks of 2Mbits (64K words x 32-bits)

- ADSP-TS203S has 4Mbits of on-chip embedded DRAM memory, divided into four blocks of 1Mbit (16K words x 32-bits)

- On all variants, each block can store program memory, data memory or both

- On-chip DMA controller is 14 DMA channels, provides zero-overhead data transfers without processor intervention

- External port is 64 bits wide and runs up to 125MHz [3]

References:

- https://www.seminarsonly.com/computer%20science/The%20Tiger%20SHARC%20processor.php

- https://www.seminarsonly.com/computer%20science/The%20Tiger%20SHARC%20processor.php

- https://www.mouser.in/new/analog-devices/adi-tigersharc-processors/

Cite this article:

Thanusri swetha J (2021),Overview of the tiger SHARC Processor, Anatechmaz, pp. 75